## 170/220 MHz High Performance Palette DAC

## **Product Description**

The RGB524™ High Performance Palette DAC from IBM brings the high quality and advanced capabilities of the previous generation RGB525 to a more compact package footprint, reducing the board real-estate required for the design of high-resolution true-color graphics subsystems.

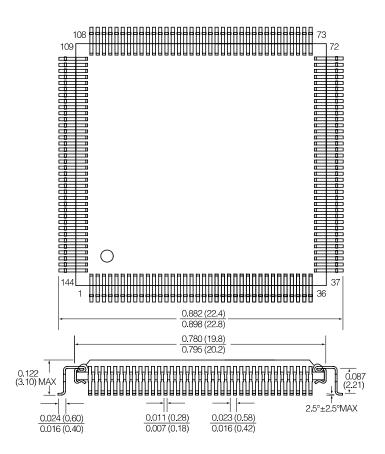

Implemented in IBM's CMOS technology, the RGB524 combines a complete list of advanced features into one 144-pin QFP package: 64-bit pixel data path, packed 24-bit pixels, two on-chip programmable clock generators, video clocks up to 220 MHz, on-chip 64x64 hardware cursor, triple monotonic 8-bit DAC's to display 16.8 million colors.

Like the RGB525, the RGB524 displays true color at 1280x1024 resolution with only 4-Megabytes of video memory.

The RGB524 provides vibrant color with unsurpassed image stability and bright, flicker-free display on large, high-resolution monitors.

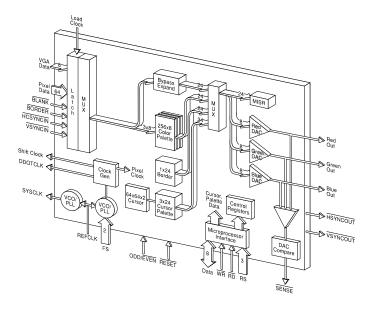

## **Functional Block Diagram**

## **Product Highlights**

- ☐ 170, 220 MHz operation

- □ RGB624 pin and register compatible

- □ RGB525 register compatible

- ☐ 64/32-bit wide pixel data bus

- ☐ Display modes up to 1600x1280

- ☐ Large Screen ISO-compliant refresh rates

- ☐ Packed 24-bit pixels

- □ 4/8/16/24/32-bits per pixel

- □ Direct color

- □ Gamma correction

- □ 256-shade gray scale

- ☐ Three 256x8 color palette RAMs

- □ Anti-sparkle circuitry

- ☐ Per-pixel palette bypass control

- □ Palette paging

- ☐ Triple monotonic 8-bit DACs

- ☐ Two on-chip clock generators

- ☐ 64x64/32x32 advanced-function hardware cursor

- ☐ 100 MHz 8-bit VGA data input

- □ 24-bit color border

- ☐ On-chip diagnostic functions

- ☐ Low-power 3.3V operation

- ☐ 5V-tolerant inputs

- □ Power-down modes

- ☐ 144-pin QFP package

- □ 0.8 μm CMOS

## **Applications**

- □ Graphical user interfaces

- □ Business graphics

- □ Video playback and post-processing

- □ Games and virtual reality

- □ CAD/CAM

- ☐ Medical Imaging

- □ Scientific Visualization

# **Table of Contents**

| 1.0 | Micr | oprocessor Access             | 1  | 4.0 | Con  | ntrols                               | 16 |

|-----|------|-------------------------------|----|-----|------|--------------------------------------|----|

|     | 1.1  | VGA Access                    |    |     | 4.1  | Blank and Border Control             | 16 |

|     |      | 1.1.1 Palette                 | 1  |     | 4.2  | Blanking Control                     | 16 |

|     |      | 1.1.2 Palette Write           | 1  |     | 4.3  | Vertical Blanking                    | 16 |

|     |      | 1.1.3 Palette Read            | 2  |     | 4.4  | Border Control                       |    |

|     |      | 1.1.4 6/8 Bit Palette Access  | 2  |     | 4.5  | Sync Control                         |    |

|     |      | 1.1.5 Palette Clocking        |    |     | 4.6  | Clocking and Pipeline Delay          |    |

|     |      | 1.1.6 Palette Access Status   |    |     |      | 4.6.1 Horizontal Sync                |    |

|     |      | 1.1.7 Pixel Mask              |    |     |      | 4.6.2 Vertical Sync                  |    |

|     | 1.2  | Indexed Access                |    |     |      | 4.6.3 Composite Sync                 |    |

|     |      | 1.2.1 Cursor Array            |    |     |      | 4.6.4 Horizontal Position Control    |    |

|     | ٥.   | ·                             |    |     | 4.7  | Additional Sync Control              |    |

| 2.0 |      | king                          |    |     | 4.8  | 24 Bit Packed Pixel Control          | 18 |

|     | 2.1  | Clock Generators              | _  |     | _    |                                      |    |

|     | 2.2  | PLL Input                     |    | 5.0 |      | sor Operation                        |    |

|     |      | 2.2.1 REFCLK                  |    |     | 5.1  | Cursor Enable                        |    |

|     | 2.3  | SYSCLK PLL Output             |    |     | 5.2  | Cursor Array                         |    |

|     | 2.4  | Pixel PLL Outputs             |    |     |      | 5.2.1 Cursor Array Access            |    |

|     | 2.5  | SCLK                          | 4  |     |      | 5.2.2 Cursor Array Writes            |    |

|     |      | 2.5.1 DDOTCLK                 | 4  |     |      | 5.2.3 Cursor Array Reads             |    |

|     | 2.6  | Additional Clocks             | 5  |     | 5.3  | Cursor Modes                         |    |

|     |      | 2.6.1 Load Clock              | 5  |     | 5.4  | Cursor Hot Spot                      |    |

|     |      | 2.6.2 Pixel Clock (Dot Clock) | 5  |     | 5.5  | Cursor Position                      | 20 |

|     | 2.7  | PLL Setup and Reset           | 5  |     | 5.6  | Interlace                            | 20 |

|     |      | 2.7.1 Pixel PLL               | 5  |     | 5.7  | Cursor Update and Display            | 20 |

|     |      | 2.7.2 SYSCLK PLL              | 5  |     |      | 5.7.1 Position                       | 20 |

|     | 2.8  | PLL Programming               | 6  |     |      | 5.7.2 Controls                       | 20 |

|     | 2.9  | PLL Frequency Selection       | 7  |     |      | 5.7.3 Other                          | 21 |

|     | 2.10 | Direct Programming            | 8  |     | D.4. | 2 Camtual                            | 04 |

|     | 2.11 | M/N Programming               |    | 6.0 |      | C Control                            |    |

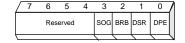

|     | 2.12 | General PLL Programming       |    |     | 6.1  | SOG - Composite Sync-On-Green        |    |

|     | 2.13 | PLL Interaction               |    |     | 6.2  | BRB - Blank Red and Blue DACs        |    |

|     | 2.14 | Glitching on Frequency Change | 9  |     | 6.3  | DSR - DAC Slew Rate                  |    |

|     | 2.15 | Diagnostic Readback           |    |     | 6.4  | DPE - DAC Blanking Pedestal Enable . | 21 |

| 3.0 | Mod  | es of Operation               | 10 | 7.0 | Pov  | ver Management                       | 22 |

| 5.0 | 3.1  | Bit Ordering                  |    |     | 7.1  | DAC Power                            | 22 |

|     | 3.2  | VGA Port                      |    |     | 7.2  | Driver Power                         | 22 |

|     | 3.3  | VRAM Pixel Port               |    |     | 7.3  | Clocking Power                       | 22 |

|     | 5.5  | 3.3.1 4 BPP                   |    |     | 7.4  | PLL Power                            |    |

|     |      | 3.3.2 8 BPP                   |    |     |      |                                      |    |

|     |      | 3.3.3 16 BPP                  |    | 8.0 |      | gnostic Support                      |    |

|     |      |                               |    |     | 8.1  | Data Masks                           |    |

|     |      | 3.3.4 24 BPP                  |    |     | 8.2  | MISR                                 |    |

|     | 2.4  | 3.3.5 32 BPP                  |    |     | 8.3  | DAC Comparators                      | 23 |

|     | 3.4  | 6 Bit Linear Palette Output   |    |     |      |                                      |    |

|     | 3.5  | Pixel Format Table            | 14 |     |      |                                      |    |

| 0.0 | Internal Register - Summary              | 24   |            | 10.2.5 Cursor                              |      |

|-----|------------------------------------------|------|------------|--------------------------------------------|------|

| 0.0 | Register Descriptions                    | 26   |            | Cursor Control                             |      |

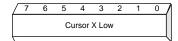

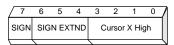

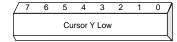

| 0.0 | 10.1 Direct Access Registers             |      |            | Cursor X Low                               |      |

|     | Palette Address (Write Mode)             |      |            | Cursor X High                              |      |

|     | Palette Data                             |      |            | Cursor Y Low                               |      |

|     | Pixel Mask                               |      |            | Cursor Y High                              |      |

|     | Palette Address (Read Mode) / Palette Ad |      |            | Cursor Hot Spot X                          |      |

|     | cess State                               |      |            | Cursor Hot Spot Y                          |      |

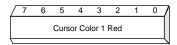

|     | Index Low                                |      |            | Cursor Color 1 Red                         |      |

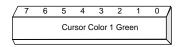

|     | Index High                               |      |            | Cursor Color 1 Green                       |      |

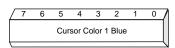

|     | Index High                               |      |            | Cursor Color 1 Blue                        |      |

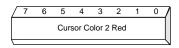

|     | Index Control                            |      |            | Cursor Color 2 Red                         |      |

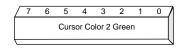

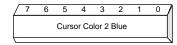

|     | 10.2 Indexed Registers                   |      |            | Cursor Color 2 Green                       |      |

|     | 10.2.1 Miscellaneous Control             |      |            | Cursor Color 2 Blue                        |      |

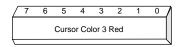

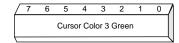

|     | Miscellaneous Control 1                  |      |            | Cursor Color 3 Red                         |      |

|     | Miscellaneous Control 2                  |      |            | Cursor Color 3 Green                       |      |

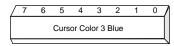

|     | Miscellaneous Control 3                  |      |            | Cursor Color 3 Blue                        |      |

|     | Miscellaneous Clock Control              |      |            | 10.2.6 Border Color                        |      |

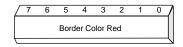

|     | Sync Control                             |      |            | Border Color Red                           |      |

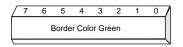

|     | Horizontal Sync Control                  |      |            | Border Color Green                         |      |

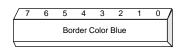

|     | Power Management                         |      |            | Border Color Blue                          |      |

|     | DAC Operation                            |      |            | 10.2.7 Diagnostic Support                  |      |

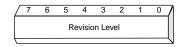

|     | Palette Control                          |      |            | Revision Level                             |      |

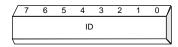

|     | System Clock Control                     |      |            | ID                                         |      |

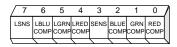

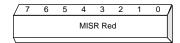

|     | 10.2.2 Pixel Representation              |      |            | DAC SenseMISR Red                          |      |

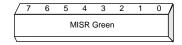

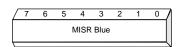

|     | Pixel Format                             |      |            | MISR Green                                 | _    |

|     | 8 Bit Pixel Control                      | -    |            |                                            | _    |

|     | 16 Bit Pixel Control                     |      |            | MISR Blue<br>PLL VCO Divider Input         |      |

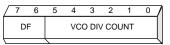

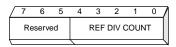

|     | 24 Bit Packed Pixel Control              |      |            | PLL Reference Divider Input                |      |

|     | 32 Bit Pixel Control                     |      |            | VRAM Mask Low                              |      |

|     | 10.2.3 Pixel Clock Frequency Selection   |      |            | VRAM Mask High                             |      |

|     | Pixel PLL Control 1                      |      |            | •                                          |      |

|     | Pixel PLL Control 2                      |      | 11.0       | Pin Descriptions                           | . 50 |

|     | Fixed Pixel PLL Reference Divider        | . 39 |            |                                            |      |

|     | F0-F15: Pixel Frequency 0 to             |      |            | Electrical and Timing Specifications       |      |

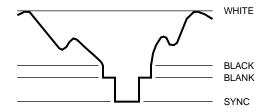

|     | Frequency 15                             |      | 13.0       | Video Waveforms                            | . 59 |

|     | 10.2.4 System Clock Frequency Selection  |      | 14.0       | Package Information                        | . 60 |

|     | System PLL Reference Divider             | . 41 | 15.0       | Ordering Information                       | . 60 |

|     | System PLL VCO Divider                   | . 41 |            | Change Summary                             |      |

|     |                                          |      |            | -                                          |      |

|     |                                          |      | Appe       | ndix                                       |      |

|     |                                          |      | <b>A.0</b> | Relationship to RGB624                     | . 62 |

|     |                                          |      | B.0        | Relationship to Previous Generation RGB525 | . 63 |

|     |                                          |      | C.0        | Switching Into VGA Mode                    | . 64 |

D.0 -A Revision Level ...... 65

# **List of Tables**

| Table 1.  | I/O Addresses                    | 1  |

|-----------|----------------------------------|----|

| Table 2.  | SCLK Frequencies                 | 4  |

| Table 3.  | PLL Equations                    | 6  |

| Table 4.  | Pixel PLL Control 1 EXT/INT      |    |

|           | Freq. Selection                  | 7  |

| Table 5.  | Direct Programming Reference     |    |

|           | Divider Values                   | 8  |

| Table 6.  | PLL Direct Programming Equations | 8  |

| Table 7.  | Pixel Format Table               | 15 |

| Table 8.  | Cursor Modes                     | 21 |

| Table 9.  | Internal Register Summary        | 24 |

| Table 10. | Pin Descriptions                 | 50 |

| Table 11. | Signal List by Pin Number        | 55 |

| Table 12. | Recommended Operating Conditions | 56 |

| Table 13. | Absolute Maximum Ratings         | 56 |

| Table 14. | DC Characteristics               | 56 |

| Table 15. | AC Characteristics               | 57 |

| Table 16. | Composite Video Output Waveform  | 59 |

| Table 17. | Composite Video Output Waveform  | 59 |

| Table 18. | Part Numbers                     | 60 |

| Table 19. | Summary of Changes               | 61 |

# **List of Figures**

| SCLK for 24 BPP Packed                 | 4                      |

|----------------------------------------|------------------------|

| 24 BPP Packed Pixel Input from VRAM    | 12                     |

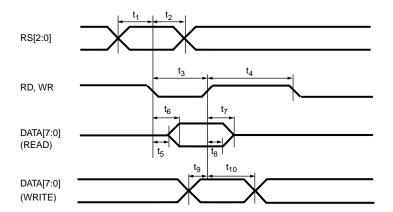

| Microprocessor Interface Timing        | 58                     |

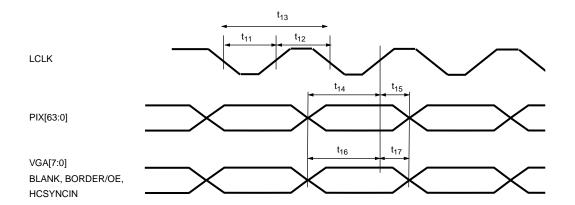

| Pixel Data and Video Control Interface |                        |

| Timing                                 | 58                     |

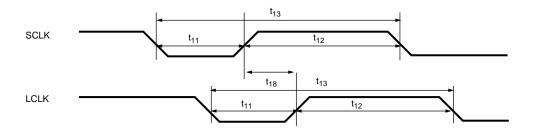

| SCLK and LCLK Timing                   | 58                     |

|                                        | SCLK for 24 BPP Packed |

v March 17, 1995

## 1.0 Microprocessor Access

As seen on the microprocessor bus there are eight I/O addresses, selected by RS[2:0]. Two indirect schemes are used to access all of the internal registers and arrays through these eight primary I/O addresses.

The first scheme is standard VGA, and operates when RS[2] = 0. Of the four I/O addresses then available with RS[1:0], only one address directly accesses a register, the Pixel Mask. The other three addresses are used to indirectly access the three  $256 \times 8$  palettes.

The second scheme is an indexed scheme and is used to access all of the remaining registers including the cursor array. This scheme operates when RS[2] =1. Of the four I/O addresses then available using RS[1:0], two are used to load an index register (Low and High). The third address is used to write or read the register or array position pointed to by the index register. The fourth address is used to directly access a register which controls whether the index register automatically increments following an indexed register access.

The eight I/O addresses selected by RS[2:0] are listed in Table 1 below:

| RS[2:0] | Register                       |

|---------|--------------------------------|

| 000     | Palette Address (Write Mode)   |

| 001     | Palette Data                   |

| 010     | Pixel Mask                     |

| 011     | Palette Address (Read Mode)    |

| 100     | Index Low                      |

| 101     | Index High                     |

| 110     | Index Data (Indexed Registers) |

| 111     | Index Control                  |

Table 1. I/O Addresses

## 1.1 VGA Access

#### 1.1.1 Palette

Internally the three 256x8 palettes are accessed by the microprocessor as a single 256x24 palette, with all 24 bits written or read in one operation.

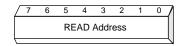

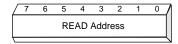

A single Palette Address register points to 1 of 256 locations for writing or reading the 24 bits. Two different Register Select addresses are used to access the Palette Address register.

A write to RS[2:0] = 000 (Palette Address Write Mode) initializes the palette logic for write operations. Subsequent writes to Palette Data (RS[2:0] = 001) will load internal palette color registers and cause these register contents to be written into the palettes.

A write to RS[2:0] = 011 (Palette Address Read Mode) initializes the palette logic for read operations. Data from the palettes will be loaded into internal palette color registers. Subsequent reads from Palette Data (RS[2:0] = 001) will read these palette color registers.

Every three accesses of Palette Data (RS[2:0] = 001) will cause the Palette Address register to be incremented. An increment past 0xff will "wrap around" to 0x00.

A read from either Palette Address (Write Mode) or Palette Address (Read Mode) will read the Palette Address register. The same register is used for writing and reading, thus, changing modes destroys the contents of the previous mode's palette address. For example, if some reads are performed and then Palette Address (Write mode) is written, the read address will be lost and a read of either Palette Address (Write Mode) or Palette Address (Read Mode) will produce the same result: the address that was written into Palette Address (Write Mode).

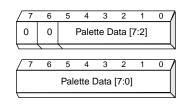

#### 1.1.2 Palette Write

Palette writes must be initialized by writing the Palette Address (Write Mode) register. This provides a starting address for writes and initializes the internal circuitry for palette write operations.

Palette writes are then performed by writing to Palette Data in a red, green, blue... sequence. These writes will load internal palette data registers in sequence. Immediately following every third write, an internal write will be triggered to the palette of the 24 bits contained in the internal palette data registers, at the address contained in the Palette Address register.

Immediately following the internal palette write triggered by the third write to Palette Data, the Palette Address register will be incremented. Thus, continuous writes to Palette Data will load the palette, stepping through the palette addresses in ascending order.

#### 1.1.3 Palette Read

Palette reads must be initialized by writing the Palette Address (Read Mode) register. This provides a starting address for reads and initializes the internal circuitry for palette read operations.

Immediately following the writing of Palette Address (Read Mode), a read of the palette will be performed at the address just written. Internal palette data registers are loaded with the read data, and the Palette Address register is incremented.

Palette reads are then performed by reading from Palette Data. Red, green, blue... data from the preloaded internal registers will be presented in sequence. Immediately following every third read, an internal read of the palette to the 24 bits contained in the internal registers will be performed at the address contained in the Palette Address register.

Immediately following the internal palette read triggered by the third read of Palette Data, the Palette Address register will be incremented. Thus, continuous reads of Palette Data will read the palette, stepping through the palette addresses in ascending order.

#### 1.1.4 6/8 Bit Palette Access

The original VGA had 6-bit DACs and 6-bit palette entries, and the low order 6 bits from/to the microprocessor port were written/read into the palette.

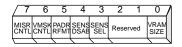

For RGB524, the DACs and palette entries are 8 bits. For non-VGA emulation all 8 bits are used. To emulate 6-bit VGA operation the upper 6 bits of the palette hold the VGA 6-bit color and the two low order bits are set to 00. The COL RES bit (color resolution) of the Miscellaneous Control 2 register determines if the access is 6-bit or 8-bit.

The reset condition is to emulate VGA using the 6 low order microprocessor data bits. COL RES is set to 6 bits. In this mode, for writing, microprocessor bits [7:6] are discarded, bits [5:0] are shifted to bits [7:2], and bits [1:0] are set to 00 before being written into the internal data registers. For reading, the internal data register bits [7:2] are shifted to bits [5:0], and bits [7:6] are set to 00 before being presented on the microprocessor data signals.

If COL RES is set to 8 bits then all 8 bits from/to the microprocessor will be written to and read from the color palette registers.

Note that the 6-to-8 bit translation is only done between the microprocessor port and the internal data registers. Internally, on writes, all 8 bits of the internal registers are written to the palette, and on reads, the internal registers retain all 8 bits read from the palette. Thus, if the palette is loaded with 8-bit values with COL RES set to 8 bits, and then the palette is read with COL RES set to 6 bits, the internal palette color registers will still be loaded with the 8 bits that were written into the palette. But the data read on the microprocessor data lines will be 6 bits.

## 1.1.5 Palette Clocking

Palette accesses are synchronized internally with the pixel clock. On writes, the pixel values of the previous cycle are held and displayed during the write cycle. Both of these features minimize disturbance of displayed pixels when the palette is accessed (anti-sparkle).

The pixel clock (as selected by the PCLK SEL bits in Miscellaneous Control 2) must be running for palette access to be valid.

The timings for the microprocessor signals are specified in units of pixel clocks. These specifications are derived from the requirement for the pixel clock to be running for palette access, as well as to allow time for the Palette Accesses and Palette Address increments to occur internally following a palette access.

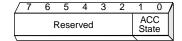

#### 1.1.6 Palette Access Status

The original VGA logic had an override for read accesses of the Palette Address (Read Mode) register. Instead of reading the Palette Address register, a value was returned that indicates the status of the last palette access, write or read.

The reset condition of RGB524 is to return the address value for a read of Palette Address (Read Mode). The VGA logic may be emulated by setting the RADR RFMT bit in Miscellaneous Control 1. This causes the status of the last palette access to be returned.

The value of the status returned is 0x00 if the last write to Palette Address was Write Mode, and 0x03 if the last write to Palette Address was Read Mode.

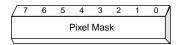

#### 1.1.7 Pixel Mask

The pixel mask is an 8-bit register addressed with RS[2:0] = 010. It can be accessed at any time without disturbing a palette write or read sequence.

Accesses to the pixel mask are asynchronous to the pixel clock. Temporary color disturbances can be expected if the mask is changed while displaying pixels through the palette.

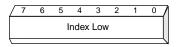

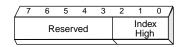

### 1.2 Indexed Access

The cursor array and a number of control registers are addressed with an internal 11-bit index register. The microprocessor accesses this as Index High (RS[2:0] = 101) and Index Low (RS[2:0] = 100).

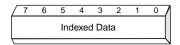

A write or read to Index Data (RS[2:0] = 110) actually writes or reads the register/cursor array location addressed by the Index register.

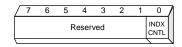

Following a write or read of Index Data, the index register will increment if the INDX CNTL bit is set. The Index Control register (RS[2:0] = 111) contains this bit. To allow for future expansion, wraparound from 0x07ff to 0x0000 is **not** supported.

In general, access of Index Low, Index High, Index Control, or any of the Indexed registers is independent of the palette access and will not disturb a palette write or read sequence. However, as described above the PADR RFMT bit in Miscellaneous Control 1, the COL RES bit in Miscellaneous Control 2, and the 6BIT ACC bit in Palette Control all affect palette access.

Also, as described above, the pixel clock must be running for valid access of the palette, and the pixel clock is affected by a number of indexed registers.

## 1.2.1 Cursor Array

In general, the indexed registers may be written or read at any time, using the address held in Index High and Index Low. This address may be set by writing to Index High or Index Low, or the value may result from the auto-increment action of a previous access.

However, as described in section 5.2.3 Cursor Array Reads on page 19, to access the cursor array a write to Index High or Index Low must be performed first. That is, the cursor array cannot be accessed by auto-increment from address 0x00ff to 0x0100.

Also, as with the palette, the pixel clock must be running to access the cursor array.

## 2.0 Clocking

#### 2.1 Clock Generators

There are two on-board clock generators: pixel clock and system clock (SYSCLK). Each clock generator uses a separate programmable phase locked loop (PLL).

The pixel clock generator provides the fundamental "dot" timings; it serves generally as the clock both for internal chip clocking and for on-card CRT timings.

The system clock generator is provided for the convenience of the graphics subsystem design. No internal use is made of this clock; the clock generator simply drives the SYSCLK output of the chip.

## 2.2 PLL Input

#### 2.2.1 **REFCLK**

The REFCLK input is a reference clock that the PLLs use in conjunction with programming registers to produce a wide variety of frequencies.

In general, REFCLK can be any frequency from 2 MHz through 100 MHz.

As discussed below, following a reset the PLL driving the SYSCLK output is enabled with the start-up frequency:

SYSCLK frequency =  $(33/16) \times REFCLK$  frequency

If it is important to have a particular frequency on SYSCLK following a reset, then the REFCLK frequency must be chosen that produces the desired SYSCLK frequency.

Also, when the "direct programming" method is used to program the PLL frequencies (see below), then REFCLK must lie on a 2 MHz boundary in the range of 4 MHz through 62 MHz (4 MHz, 6 MHz, 8 MHz,... 62 MHz).

## 2.3 SYSCLK PLL Output

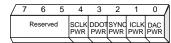

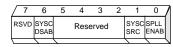

The system clock PLL drives the SYSCLK output. Two bits in the System Clock Control register affect this output. Bit 6, SYSC DSAB, is used to 3-state the driver. Bit 1, SYSC SRC, is used to bypass the SYSCLK PLL (the incoming REFCLK is steered to the SYSCLK output).

The supported frequency range for SYSCLK is 16.25 MHz to 100 MHz.

## 2.4 Pixel PLL Outputs

The pixel PLL is used internally as the pixel clock. The maximum allowed generated frequency is 170/220 MHz, dependent on the product version.

The pixel PLL Output is not available directly. However, two divided versions are provided as output signals:

- □ SCLK

- □ DDOTCLK

## 2.5 SCLK

SCLK (Serial Clock) is intended for clocking of the serial outputs of the VRAMs to the pixel port inputs. As such, the divide factor is a function of the VRAM pixel port width (64 or 32 bits), and the number of pixels contained in an access. For example, with a VRAM width of 64 and operating at 16 bits-per-pixel, there will be 64/16=4 pixels brought in with each VRAM access, and SCLK will operate at 1/4 the frequency of the pixel PLL output.

If the VGA port is selected SCLK will simply be the output of the pixel PLL. Table 2, "SCLK Frequencies," is a table of all the SCLK frequencies that are produced.

**Table 2. SCLK Frequencies**

| BPP       | VRAM=32 | VRAM=64 |  |  |  |

|-----------|---------|---------|--|--|--|

| 4         | ÷ 8     | ÷ 16    |  |  |  |

| 8         | ÷ 4     | ÷ 8     |  |  |  |

| 15/16     | ÷ 2     | ÷ 4     |  |  |  |

| 32        | ÷ 1     | ÷ 2     |  |  |  |

| 24 Packed | Invalid | ÷ (8/3) |  |  |  |

| VGA       | ÷ 1     |         |  |  |  |

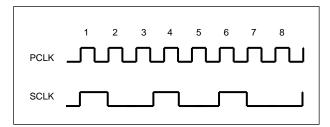

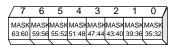

"24 Packed" is a special case. It is only valid with a VRAM width of 64, and it produces 3 SCLKs for every 8 internal pixel clocks as shown in Figure 1.

Figure 1. SCLK for 24 BPP Packed

The SCLK output can be inverted with the SCLK INVT bit of the Miscellaneous Clock Control register. This allows either polarity to be used, as desired, to aid in meeting critical timings at the card level.

The SCLK DSAB bit of the Miscellaneous Clock Control register can be used to 3-state the SCLK output if desired.

## 2.5.1 DDOTCLK

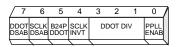

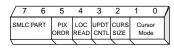

DDOTCLK (Divided Dot Clock) is simply the pixel PLL output divided by 1, 2, 4, 8 or 16 as determined by the DDOT DIV bits of the Miscellaneous Clock Control register.

Note that the maximum supported output frequency of DDOTCLK is 100 MHz, so some values of the DDOT DIV bits will become illegal when the pixel PLL is programmed to operate beyond this frequency.

When a pixel format of 24 BPP Packed is selected, the SCLK output may be driven on DDOTCLK instead of the divided pixel PLL output, under control of the B24P DDOT bit of the Miscellaneous Clock Control register.

DDOTCLK is similar to the SYSCLK output in that it is provided for general card use and is not used internally. However, its frequency is slaved to the pixel clock, whereas SYSCLK is independent. The DDOTCLK may be 3-stated with the DDOT DSAB bit of the Miscellaneous Clock Control register if desired.

**Note:** Although DDOTCLK and SCLK are both derived from the pixel clock. there is otherwise no particular relationship between the two clocks. In particular, the two clocks do not have any associated phase relationship.

#### 2.6 Additional Clocks

#### 2.6.1 Load Clock

The LCLK input (Load Clock) is used to latch up all incoming pixel data and video controls. The maximum frequency of this input is 100 MHz.

## 2.6.2 Pixel Clock (Dot Clock)

The pixel clock, or dot clock, is the internal clock used to clock pixel data up through the DACs. It is also required to be running to access the palette and the cursor. The maximum frequency of this clock is 170/220 MHz (depending on the chip version).

There are several sources of the pixel clock, as selected by the PCLK SEL bits in the Miscellaneous Control 2 register:

**LCLK input** This is the reset default. It is intended to be used when the VGA port is selected as the pixel source.

**Pixel PLL output** This is intended to be used when the VRAM pixel port is selected as the pixel source. It provides the highest pixel clock operation.

**REFCLK input** This is intended for laboratory bringup.

When LCLK is selected as the pixel clock all internal pixel operations are synchronous with LCLK. If the pixel clock is sourced by the pixel PLL output or REF-CLK, then the incoming pixels and video controls are expected to be derived from SCLK. After latching the signals with LCLK, the signals are clocked with an internal SCLK, and then clocked with the internal pixel clock. LCLK must maintain a specified relationship to SCLK to achieve the internal transfer of the clocking from LCLK to SCLK.

## 2.7 PLL Setup and Reset

## 2.7.1 Pixel PLL

The PLL is enabled for running at a programmed frequency by setting the REF DIV COUNT, VCO DIV COUNT, and DF bits (as described in the following sections), and then setting the PLL ENAB bit of the Miscellaneous Clock Control register.

When the PLL ENAB bit is 0 (off), the PLL will continue to run but the frequency will not be determined by programming values. The PLL will drive to its lowest frequency of operation, in the range of 5 KHz to 250 KHz.

The pixel clock frequency is determined by the DF programming bits. When DF = 00, the pixel clock is equal to the PLL clock divided by 4 (1.25 KHz to 62.5 KHz). When DF = 01 the pixel clock equals the PLL clock divided by 2 (2.25 KHz to 125 KHz), and when DF = 10 or 11, the pixel clocks equals the PLL clock (5 KHz to 250 KHz.)

Following a reset, the PLL ENAB bit is off and the DF bits of all programming registers are set to 00, so the pixel clock will be PLL clock/4 = 1.25 KHz to 64.25 KHz.) The PORT SEL bit of Miscellaneous Control 2 register will be 0 (VGA port), which will cause the SCLK output to be the same as the pixel clock (1.25 KHz to 64.25 KHz.) The DDOT DIV bits of the Miscellaneous Clock Control register will be zero, which will cause DDOT-CLK to also be the same frequency as the pixel clock.

#### 2.7.2 SYSCLK PLL

The SYSCLK PLL is enabled with the SPLL ENAB bit of the System Clock Control register. Unlike the pixel PLL, following a reset, this ENAB bit will be set, and the SYSCLK PLL will be running and driving the SYSCLK driver. The output frequency will be  $(33/16)\times REFCLK$ .

When the SPLL bit is 0 (disabled) the SYSCLK PLL will run in the 5 KHz to 250 KHz range similar to the pixel PLL. The frequency driven on the SYSCLK output will be determined by the value of the DF bits in the System PLL VCO Divider register), using the same divide factors as described above for the pixel PLL.

| DF | Output Frequency            | Internal VRF        | Max Output Freq. (MHz) |         |  |

|----|-----------------------------|---------------------|------------------------|---------|--|

| DI | Output Frequency            | internal VKF        | 170                    | 220     |  |

| 00 | FREF × (VCO DIV COUNT + 65) | FREF                | 42.5                   | 55.0    |  |

| 00 | (REF DIV COUNT) × 8         | (REF DIV COUNT) × 2 | 42.3                   | 33.0    |  |

| 01 | FREF × (VCO DIV COUNT + 65) | FREF                | 85                     | 110 (*) |  |

| UI | (REF DIV COUNT) × 4         | (REF DIV COUNT) × 2 | 63                     | 110 ( ) |  |

| 10 | FREF × (VCO DIV COUNT + 65) | FREF                | 170 (*)                | 220 (*) |  |

| 10 | (REF DIV COUNT) × 2         | (REF DIV COUNT) × 2 | 170()                  | ۵۵U (*) |  |

| 11 | FREF × (VCO DIV COUNT + 65) | FREF                | 170 (*)                | 220 (*) |  |

| 11 | REF DIV COUNT               | REF DIV COUNT       | 170()                  | ۵۵U (*) |  |

Table 3. PLL Equations

## 2.8 PLL Programming

The two PLLs are programmed identically. Three values are used:

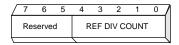

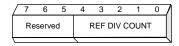

**REF DIV COUNT (Reference Divide Count)** This number provides a count value for dividing down the incoming REFCLK. It must be between 2 and 31. Operation of the PLL is indeterminate if this number is 0 or 1.

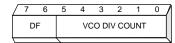

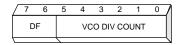

## VCO DIV COUNT (VCO Divide Count) This

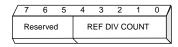

number provides a count value for the divider in the PLL feedback loop. The value can range from 0 through 63. Internally, 65 is added to VCO DIV COUNT, so that the PLL feedback divider value ranges from 65 through 128.

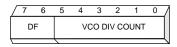

**DF** (**Desired Frequency**) These are two bits with values of 00, 01, 10, and 11. The intent of these bits is to divide the operation of the PLL into four frequency ranges. Following the divide of the REFCLK provided by the REF DIV COUNT there is an additional divide-by-two which is selected or bypassed with the DF bits. Also, the output of the PLL has a divider stage, or postscaler, that is controlled by the DF bits.

Table 3, "PLL Equations," gives the general formulas for programming the PLLs. Because of the action of the DF bits there are four equations, one for each DF bit setting.

It is possible to program the PLLs with values that generate illegal operating conditions:

- The reference frequency VRF (Video Reference Frequency), which is internal to the PLL, cannot be less than 1 MHz.

- The internal VCO (Voltage Controlled Oscillator) cannot exceed the rated speed of the product (170/220 MHz).

- The SYSCLK output driven by the SYSCLK PLL cannot exceed 100 MHz.

- The DDOTCLK output driven by the pixel PLL cannot exceed 100 MHz.

Table 3, "PLL Equations," gives the equations for calculating the internal VRF. Table 3 also gives the maximum allowable output frequency for each setting of DF. This reflects the action of the VCO postscaler. If the PLLs are programmed so that these maximum dot clock frequencies are not exceeded then the maximum VCO frequency will not be exceeded.

<sup>1.</sup> FREF = REFCLK frequency

<sup>2.</sup> Frequencies marked with (\*) are maximum pixel PLL frequencies. The SYSCLK PLL maximum output frequency is 100 MHz.

## 2.9 PLL Frequency Selection

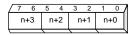

The REF DIV COUNT, VCO DIV COUNT, and DF bits are provided to the PLLs in a pair of 8-bit registers. REF DIV COUNT is 5 bits and occupies one register, with the 3 high order bits unused. The 6 VCO DIV COUNT bits occupy the second register, with the 2 high order bits used by DF.

For the SYSCLK PLL, the two programming registers are the System PLL Reference Frequency, which holds REF DIV COUNT, and the System PLL VCO Divider, which holds VCO DIV COUNT and the DF bits.

For the pixel PLL, there are actually 17 registers which can be used to hold the programming values: Fixed Pixel PLL Reference Divider and F0 - F15. A pair of registers is selected from this group to provide the pixel PLL programming values. This selection is controlled by the pixel PLL Control 1 and pixel PLL Control 2 registers.

Two different programming styles are supported:

**Direct Programming** In this scheme only the register holding VCO DIV COUNT and DF is altered to change the frequencies. The register for REF DIV COUNT holds a value that is constant for all frequencies. This method is discussed in more detail below.

M over N In this scheme both register values are changed to program a new frequency. The name refers to the general PLL concept in which

Output frequency = Input reference  $\times$  (M/N)

where VCO DIV COUNT serves as M and REF DIV COUNT serves as N, with modifications to the equation as shown in Table 3, "PLL Equations."

For the SYSCLK PLL there is not much distinction between the two programming styles. Both registers are written to provide an initial operating frequency. Then to change frequency either one register is changed (System PLL VCO Divider), or both registers are changed, depending on the programming style.

For the pixel PLL, a set of preprogrammed frequencies can be stored in the F0 - F15 registers, and the number of stored frequencies depends on the programming style.

When the direct programming style is used a single REF DIV COUNT is stored in the Fixed PLL Reference Divider register. Up to 16 values of VCO DIV COUNT and DF can be stored in the F0 - F15 registers, allowing 16 preprogrammed pixel clock frequencies.

With the M/N style the Fixed Pixel PLL Reference Divider register is not used. The F0 - F15 are reconfigured as 8 pairs of M and N values (M0,N0,M1,N1, ... M7,N7). This allows 8 preprogrammed pixel clock frequencies.

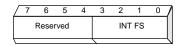

The selection of the programming registers, either 1 of the 16 F0 - F15 registers or 1 of the 8 M/N pairs, is done either externally with the FS[1:0] inputs to the module, or internally with the INT FS[3:0] bits of Pixel PLL Control 2 register. When the M/N style is used INT FS[3] is ignored.

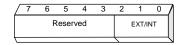

The programming style and selection source is chosen with the EXT/INT bits of the Pixel PLL Control 1 register, as shown in Table 4, "Pixel PLL Control 1 EXT/INT Freq. Selection."

Table 4. Pixel PLL Control 1 EXT/INT Freg. Selection

| EXT<br>/INT | Frequency<br>Selection | REF DIV<br>COUNT           | VCO DIV<br>COUNT, DF |  |  |  |  |  |

|-------------|------------------------|----------------------------|----------------------|--|--|--|--|--|

| 000         | External<br>FS[1:0]    | Fixed Reference<br>Divider | F0-F3                |  |  |  |  |  |

| 001         | External<br>FS[1:0]    | N0-N3                      | M0-M3                |  |  |  |  |  |

| 010         | Internal<br>FS[3:0]    | Fixed Reference<br>Divider | F0-F15               |  |  |  |  |  |

| 011         | Internal<br>FS[2:0]    | N0-N7                      | M0-M7                |  |  |  |  |  |

Note that there are more selections available with the internal register INT FS[3:0] than using the external FS[1:0] inputs. With the external inputs, only 4 frequencies can be chosen, using either direct programming or M/N. With the INT FS[3:0] bits 8 frequencies can be chosen using M/N or 16 frequencies can be chosen using direct programming.

**Table 5. Direct Programming Reference Divider Values**

| REFCLK (MHz) | Fixed PLL Reference Divider<br>Register Value |

|--------------|-----------------------------------------------|

| 4            | 0x0002                                        |

| 6            | 0x0003                                        |

| 8            | 0x0004                                        |

| 10           | 0x0005                                        |

| 12           | 0x0006                                        |

| 14           | 0x0007                                        |

| 16           | 0x0008                                        |

| 18           | 0x0009                                        |

| 20           | 0x000a                                        |

| 22           | 0x000b                                        |

| 24           | 0х000с                                        |

| 26           | 0x000d                                        |

| 28           | 0x000e                                        |

| 30           | 0x000f                                        |

| 32           | 0x0010                                        |

| 34           | 0x0011                                        |

| 36           | 0x0012                                        |

| 38           | 0x0013                                        |

| 40           | 0x0014                                        |

| 42           | 0x0015                                        |

| 44           | 0x0016                                        |

| 46           | 0x0017                                        |

| 48           | 0x0018                                        |

| 50           | 0x0019                                        |

| 52           | 0x001a                                        |

| 54           | 0x001b                                        |

| 56           | 0x001c                                        |

| 58           | 0x001d                                        |

| 60           | 0x001e                                        |

| 62           | 0x001f                                        |

## 2.10 Direct Programming

Use the following steps to calculate the values used with direct programming:

- 1. Look up the REFCLK frequency in Table 5, "Direct Programming Reference Divider Values," and write the given programming value into the PLL Reference Divider register (System PLL Reference Divider for the SYSCLK PLL, Fixed Pixel PLL Reference Divider for the pixel PLL). If the incoming REFCLK frequency does not appear in this table, then the direct programming method cannot be used.

- 2. Use Table 6, "PLL Direct Programming Equations," to determine the values to write into the VCO Divider register (System PLL VCO Divider for the SYSCLK PLL, F0 F15 for the pixel PLL). First, pick the row of the table whose frequency range covers the frequency of interest. This will determine the value of the DF bits to write. Next, use the given equation to calculate the value of the VCO DIV BITS. Write these two values together to the appropriate register.

The generated pixel clock frequency is designated in this table as VF, for Video Frequency. Note that within each range the desired VF frequency must lie on a given step value (e.g., with DF = 11 a frequency of 159 MHz is invalid because it does not lie on a 2 MHz step; but either 158 MHz or 160 MHz is valid).

**Table 6. PLL Direct Programming Equations**

| rable of the birect i regramming Equations |                     |                 |            |  |  |  |  |  |

|--------------------------------------------|---------------------|-----------------|------------|--|--|--|--|--|

| DF                                         | VCO Divide<br>Count | Frequency Range | Step (MHz) |  |  |  |  |  |

| 00                                         | (4 x VF) - 65       | 16.25 - 32 MHz  | 0.25       |  |  |  |  |  |

| 01                                         | (2 x VF) - 65       | 32.5 - 64 MHz   | 0.5        |  |  |  |  |  |

| 10                                         | VF - 65             | 65.0 - 128 MHz  | 1.0        |  |  |  |  |  |

| 11 (VF / 2) - 65 130.0 - 220 MHz 2.0       |                     |                 |            |  |  |  |  |  |

| VF = Desired Video Frequency               |                     |                 |            |  |  |  |  |  |

## 2.11 M/N Programming

For the "M over N" programming style use Table 3, "PLL Equations," in the following steps:

- Select values for REF DIV COUNT, VCO DIV COUNT, and DF that generate the desired frequency (or come close enough). Note that the values 0 and 1 are illegal for REF DIV COUNT under all conditions.

- Calculate the internal reference frequency VRF. Verify that this frequency is not less than 1 MHz.

- Verify that the dot clock frequency does not exceed the maximum value specified in the table.

- If conditions 2 and 3 are not met then the selected values cannot be used.

## 2.12 General PLL Programming

Fundamentally the only differences between the two programming styles are these:

- Direct programming can be used only if the REFCLK frequency falls on a 2 MHz boundary from 4 MHz through 62 MHz.

- With direct programming, for a given pixel clock frequency there is only one set of programming values. These values are obtained from Table 5, "Direct Programming Reference Divider Values," and Table 6, "PLL Direct Programming Equations." Illegal conditions cannot be generated as long as the correct value from Table 5, "Direct Programming Reference Divider Values," is used.

- M/N can be used with any REFCLK frequency from 2 MHz through 100 MHz

- A given pixel clock can be generated with multiple combinations of programming values. Some of these values can produce illegal internal conditions. Table 3, "PLL Equations," is used to calculate the resulting pixel clock and to determine if conditions are violated.

If the incoming REFCLK does not meet the requirements for direct programming, then M/N programming must be used for both PLLs.

If REFCLK is suitable for direct programming, then the programming style for the SYSCLK PLL is generally a matter of convenience.

For the pixel PLL, the use of preprogrammed frequencies, and the number required, 8 or 16, can affect the choice of programming styles.

However, the register selection specified with the EXT/INT bits of the Pixel PLL Control 1 register does not necessarily force the selection of programming style, direct or M/N. For example, there is nothing to prevent an arbitrary value from being written into the Fixed Pixel PLL Reference Divider and writing an appropriate value into one of the F0 - F15 registers as calculated with the M/N method. Of course, if multiple "N" values are used and they have to be re-written to the Fixed Pixel PLL Reference Divider every time the FS[3:0] value changes, this defeats the purpose of the FS[3:0] selection mechanism.

Likewise, when the 1-of-8 M/N register selection is used there is nothing to prevent using the direct programming equations from being used for the values. The same value will wind up being used for all of the "N" values.

### 2.13 PLL Interaction

The Pixel PLL and the SYSCLK PLL will interfere with each other (they will modulate the output frequency of the other PLL) if the higher frequency falls within 3 MHz of an integer multiple of the lower frequency. That is, if  $f_{higher}$  is the higher of the two frequencies and  $f_{lower}$  is the lower frequency, then the following equation must be satisfied:

$$_{higher}^{f} \neq (n \times f_{lower}) \pm 3 \text{ MHz}; n = 1,2,3...$$

## 2.14 Glitching on Frequency Change

When the operating frequency of either PLL is changed by changing one of the programming register values, the transition from the original frequency to the new frequency can either occur smoothly or can glitch, depending upon the following:

- If the DF bits are not changed, then changing the REF DIV COUNT and VCO DIV COUNT bits will not cause a glitch.

- 2. If the DF bits are changed, then the PLL output can glitch.

## 2.15 Diagnostic Readback

The read-only registers Pixel PLL VCO Divider Input and Pixel PLL Reference Divider Input contain the programming values actually used by the pixel PLL. These registers can be used to verify that the desired programming registers are the ones actually selected.

## 3.0 Modes of Operation

Pixel data can come from the VGA port or the VRAM pixel port, as selected by the PORT SEL bit of the Miscellaneous Control 2 register.

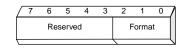

If the VRAM pixel port is selected, the pixel format can be 4 BPP (bits per pixel), 8 BPP, 15/16 BPP, 24 BPP Packed, or 32 BPP, selected by the Format bits of the Pixel Format register. Table 7, "Pixel Format Table," on page 15 shows how the input bits are selected as a function of Pixel Format.

VGA data and 4 BPP data are always used to indirectly generate 24 bits of color by indexing into the 256 entry palettes. The Pixel Mask register is used to selectively mask off the index bits as desired.

8 BPP, 15/16 BPP, 24 BPP Packed, and 32 BPP from the VRAM pixel port can either be indirect (through the palettes) or direct (bypassing the palettes).

Each of these formats has an associated control register with bits to select indirect or direct color. Additionally 15/16 BPP and 32 BPP formats allow a bit within the incoming data to dynamically select indirect or direct color.

As with VGA and 4 BPP, the Pixel Mask is used to mask off palette address bits with indirect color access for 8, 15/16, 24 Packed, and 32 BPP.

## 3.1 Bit Ordering

Bit order is high-to-low. For 8 BPP, the MSB is '7' and the LSB is '0'; for 16 BPP the MSB is '15' and the LSB is '0', and so on.

When the VRAM pixel port is selected the default condition is to access the pixels from low to high. For each LCLK, the first pixel used is at the end with bit PIX[00], and the last pixel used is at the end with bit PIX[63] (bit PIX[31] for VRAM width = 32). For example, for 8 BPP, the first pixel is PIX[07:00], the second pixel is PIX[15:08], and so on.

4 BPP is a special case. Within a byte, the default condition is to select first the high nibble (e.g., PIX[07:04]), then the low nibble (PIX[03:00]). The SWAP NIB bit of the Miscellaneous Control 3 register may be used to swap the order the two nibbles are used. This swap is applied to every byte that is read in, and is only active, when set, for 4 BPP.

### 3.2 VGA Port

VGA uses 8 bits per pixel. When the VGA port is selected only indirect mode is used. The 8 bits are masked with the Pixel Mask register and presented to the red, green, and blue palettes as indices into the 256 entries of each palette. The masked data is used as the same index into each of the three color palettes.

## 3.3 VRAM Pixel Port

## 3.3.1 4 BPP

With 4 BPP format 8 pixels (32 bit VRAM width) or 16 pixels (64 bit VRAM width) are obtained for each pixel port data access. As noted above the default access of the two pixels within each byte are high-to-low:

PIX[7:4] = pixel one

PIX[3:0] = pixel two,

but this can be reversed with the SWAP NIB bit of the Miscellaneous Control 3 register.

4 BPP is only used in indirect color mode. The 4 bits are masked with the 4 low order bits [3:0] of the Pixel Mask. The resultant masked 4 bits are then used to index into each of the red, green, and blue palettes.

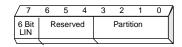

With 4 BPP the 256 entry palettes are divided into 16 partitions of 16 entries per partition. The upper 4 bits of the Pixel Mask register are ignored. The PARTITION bits of the Palette Control register are used as the upper 4 bits of the palette address to select the desired partition. The 4 masked pixel bits are used to index to 1-of-16 entries within the selected partition.

#### 3.3.2 8 BPP

With 8 BPP format 4 pixels (32 bit VRAM width) or 8 pixels (64 bit VRAM width) are obtained for each pixel port data access.

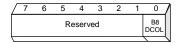

8 BPP can be indirect or direct, under control of the B8 DCOL bit of the 8 BPP Control register. If indirect, the 8 bits are masked with the Pixel Mask register and presented to the red, green, and blue palettes as indices into the 256 entries of each palette.

If direct, the 8 bits are presented to the red, green, and blue DACs. Note that since the red, green, and blue colors are identical the displayed image will be monochrome.

#### 3.3.3 16 BPP

With 15 BPP or 16 BPP format 2 pixels (32-bit VRAM width) or 4 pixels (64-bit VRAM width) are obtained for each pixel port data access. The 15 or 16 bits are expanded to 24 bits, under control of the 16 BPP Control register.

The 16 BPP Control register provides a number of options for using the 16 BPP format:

- 1. The incoming pixel can be 15 bits (555 format) or 16 bits (565 format).

- The color path can be indirect (through the palettes) or direct (bypassing the palettes). Also, with 555 format, the 16th bit can be used to dynamically switch on a pixel-by-pixel basis between indirect and direct color.

- 3. If indirect color is selected, the addressing of the palettes can be "sparse" (pixel bits used as high order palette address bits) or "contiguous" (pixel bits used as low order palette address bits).

- 4. If indirect color with contiguous addressing is selected, the palettes can be divided into partitions. The PARTITION bits of the Palette Control register are used to select the partition by filling in the upper palette address bits. With 555 format 8 partitions are available; with 565 format there are 4 partitions.

- 5. If direct color is used the pixel bits are sent to the DAC high order bits. The low order bits can be zero filled, or the low order bits can be filled with the high order bits of the pixel data. (See description of ZIB/LIN bit below.)

If dynamic bypass is selected the following conditions will apply:

- The format will be forced to 15 bit (555), with the unused 16th bit now used to control indirect/direct color selection.

- 2. The indirect color path will be forced to use sparse addressing of the palettes. Partitions cannot be used

- The direct color path will force the low order bits to the DACs to be zero filled (ZIB). LIN format cannot be used.

- 4. The Pixel Mask will mask the pixel data regardless of whether or not the palette is bypassed.

#### 3.3.3.1 555/565 Formats

The 555/565 bit determines if the pixel is 15 bits (5:5:5 format) or 16 bits (5:6:5 format). The format designator, 5:5:5 or 5:6:5, refer to the bit allocations, high-to-low, for red:green:blue.

With 15 BPP the high order bit of each two bytes (PIX[15], PIX[31], PIX[47], PIX[63]) is discarded unless dynamic bypass is specified (B16 DCOL bits = 01). With dynamic bypass, this bit is used for indirect/direct color selection.

As noted above setting the mode to dynamic bypass will force the format to 555 regardless of the setting of the 555/565 bit.

## 3.3.3.2 Color Path Selection

The B16 DCOL bits are used to select one of:

- 1. Indirect color always (00).

- 2. Direct color always (11).

- 3. Dynamic selection of indirect or direct color (01).

The expansion to 24 bits varies depending on whether the color path is indirect or direct.

Indirect Color: The palette addressing can be sparse or contiguous and is controlled by the SPR/CNT bit. With sparse addressing the pixels will address 32 locations each for the red and blue palettes, and 32 locations for green in 555 format or 64 locations for green in 565 format. With the lower address bits set to zeroes the locations accessed will be "scattered" through the palettes, with the intermediate locations unused.

With contiguous addressing the PARTITION bits of the Palette Control register are used for the high order palette address bits, and the access within each palette is

contiguous. For 555 format there are 8 partitions and 32 entries within each partition. For 565 format there are 4 partitions. All 64 entries in the green palette are addressed. Only the lower 32 entries of the red and blue palettes are used; the high 32 entries are not used.

For sparse addressing the low order bits are dependent on the ZIB/LIN bit. This bit *must* be set to 0 (ZIB). This will force the low order bits to zeros. If ZIB/LIN is 1 (LIN) then the values of the low order bits presented to the palettes are undefined.

For sparse addressing the low order Pixel Mask bits have no effect.

For contiguous addressing the high order bits are always supplied by the PARTITION bits and the high order Pixel Mask bits have no effect.

As noted above for dynamic bypass mode the format is forced to 555 mode and addressing is forced to be sparse regardless of the setting of the SPR/CNT bit.

**Direct Color:** To expand the 5 or 6 bits of color from the pixel data to 8 bits, the ZIB/LIN bit of the 16 BPP Control register specifies the generation of the low order 3 or 2 bits. If ZIB (Zero Intensity Black), the low order bits are made 0. If LIN (Linear), the low order bits are made equal to the high order bits. This causes the 5 or 6 bits to expand to 8 bits in a linear fashion, with both zero scale and full scale values used. With Zero Intensity Black, full scale cannot be achieved.

As noted above for dynamic bypass mode the format is forced to 555 mode and the low order fill is forced as ZIB, regardless of the setting of the ZIB/LIN bit.

#### 3.3.3.3 Dynamic Bypass

As described above the selection of "dynamic bypass" mode forces the 555 format and uses the high order bit of the incoming 16-bit pixels as a control bit to select, on a pixel-by-pixel basis, the indirect (color lookup) or direct (lookup bypass) path.

The meaning of this bit depends on the BY16 bit in the 16 BPP Control register. When BY16 = 0 the incoming control bit forces the bypass. That is, when the control bit is 1 the palette is bypassed (direct color), and when 0 the palette is not bypassed (indirect color).

When BY16 = 1 the meaning of the incoming control bit is reversed; it now forces a lookup. That is, when the control bit is 1 the palette is used (color lookup), but when 0 the palette is bypassed (direct color).

#### 3.3.4 24 BPP

24 BPP Packed can only be selected when the VRAM width is 64 bits. If 24 BPP Packed format is selected with the Pixel Format register, but the VRAM SIZE bit in the Miscellaneous Control 1 register is set for 32 bits, then the product operation is undefined.

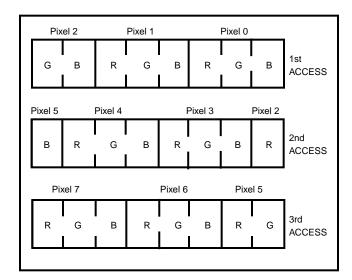

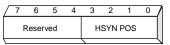

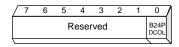

With 24 BPP Packed format each 64-bit pixel port data access contains 2+2/3 pixels. Every 3 consecutive pixel port data accesses ( $3\times8=24$  bytes) contains 8 pixels of 3 bytes each. The assignment of the bytes for each of the three accesses is shown in Figure 2 on page 12. Each byte contains 8 bits of red, green, or blue color. Color access can be indirect or direct, and is selected with the B24P DCOL bit of the 24 BPP Packed Control register.

For indirect color, the 8 bits of red, green, and blue are each masked by the Pixel mask, and then presented to the red, green, and blue palettes as indices into the 256 entries of each palette.

For direct color, the 8 bits of red, green, and blue are presented to the DACs.

Figure 2. 24 BPP Packed Pixel Input from VRAM

#### 3.3.5 32 BPP

With 32 BPP format 1 pixel (32-bit VRAM width) or 2 pixels (64-bit VRAM width) are obtained for each pixel port data access. For each 32 bits accessed, the low three bytes (24 bits) are used for the three colors, with 8 bits each for red, green, and blue.

32 BPP mode is controlled with the 32 BPP Control register. This register has the B32 DCOL bits, which are used to select one of:

- 1. Indirect color always (00).

- 2. Direct color always (11).

- 3. Dynamic selection of indirect or direct color (01).

With indirect color always or direct color always the high order byte is unused. (PIX[31:24] and PIX[63:56])

With dynamic selection (dynamic bypass), the "25th" bit is used as the indirect/direct control bit (PIX[24], PIX[56]) and the remaining bits of the high order byte are unused. (PIX[31:25] and PIX[63:57].) The pixel data in this mode is masked by the Pixel Mask regardless of whether or not the palette is bypassed.

For indirect color, the 8 bits of red, green, and blue are each masked by the Pixel mask, and then presented to the red, green, and blue palettes as indices into the 256 entries of each palette.

For direct color, the 8 bits of red, green, and blue are presented to the DACs.

## 3.3.5.1 Dynamic Bypass

As described above the selection of "dynamic bypass" mode uses the "25th" bit of the incoming 32-bit pixels as a control bit to select, on a pixel-by-pixel basis, the indirect (color lookup) or direct (lookup bypass) path.

The meaning of this bit depends on the BY32 bit in the 32 BPP Control register. When BY32 = 0 the incoming control bit forces the bypass. That is, when the control bit is 1 the palette is bypassed (direct color), and when 0 the palette is not bypassed (indirect color).

When BY32 = 1 the meaning of the incoming control bit is reversed; it now forces a lookup. That is, when the control bit is 1 the palette is used (color lookup), but when 0 the palette is bypassed (direct color).

## 3.4 6 Bit Linear Palette Output

The 6BIT LIN (6 bit linear) bit of the Palette Control register affects the format of the color data read from the palettes and presented to the DACs in indirect color mode. It only has effect when the color resolution is set to 6 bits with the COL RES bit of the Miscellaneous Control 2 register and DCOL CNTL is set to indirect color.

If the palettes contain data with the two low order bits set to 00 (which will be the case when the palettes are loaded with COL RES set to 6 bits), without special processing the data values presented to the DACs will range from 0x00 through 0xfd. The maximum output of the DACs will be approximately 1.5% less than full scale (0xff). This will occur when 6BIT LIN is set to 1.

When 6BIT LIN is set to 0 (the default), then the outputs of the palettes will be modified to allow the DACs to reach full scale output. The modification consists of discarding the two low order bits from the palettes, and substituting the two high order bits for the two low order bits presented to the DACs. (i.e., the palette bits presented to a DAC will be bits 7 6 5 4 3 2 7 6).

With this bit substitution there will be a "linear" mapping of the palette data range (0x00 – 0xfd) to the DAC data range (0x00 – 0xff), and the DACs will operate over their full range.

If COL RES = 1 (8-bit color resolution) the palette outputs are presented to the DACs unchanged, and 6BIT LIN has no effect. The DACs will operate over the 8-bit range from completely off to full scale on.

Palette linear output is intended for emulation of the VGA 6-bit DACs in which the palette is loaded with 6-bit colors in the 6 high-order bits by setting COL RES to 6-bits. However, regardless of how the palette was loaded or what the pixel format is (VGA, 4, 8, 15/16, 24, 32 BPP), if enabled (DCOL = indirect, COL RES = 6 bit, 6BIT LIN = 0) the palette outputs will be affected as discussed above.

In summary, with the default conditions for VGA mode (indirect color, 6-bit color resolution, 6BIT LIN = 0), there will be a linear mapping of the 6-bit VGA palette data to the DACs, and the DACs will operate over their full range. The mapping can be turned off by setting 6BIT LIN to 1, in which case the 8 bits from the palettes are presented to the DACs unmodified. With 00 in the two low order bits of the palettes the DACs will not reach full scale output.

With 8-bit color resolution (indirect color), or with direct color, the setting of 6BIT LIN has no effect.

## 3.5 Pixel Format Table

Table 7 shows the bit assignments of the pixel data port for each supported pixel format. Prefixes A - P identify individual pixels, and numbers 0 - 7 identify the bit within the pixel. For 4 bit pixels, this information is the data seen by the three color palettes. For 8 bit pixels, it is the data seen by the three color palettes in indirect color mode, and it is the data seen by the three DACs in direct color mode. The suffixes (blu, grn, red) identify the data seen by each of the color palettes (indirect mode) or each of the DACs (direct mode) for 16, 24, and 32 bit pixels.

**Table 7. Pixel Format Table**

| Table 7. Pixel Format Table |               |                 |          |                                  |                 |                                  |                |                |                |                |                  |

|-----------------------------|---------------|-----------------|----------|----------------------------------|-----------------|----------------------------------|----------------|----------------|----------------|----------------|------------------|

| Pixel                       | 4 B           | PP <sup>1</sup> |          |                                  | 15/16           | BPP <sup>2,3</sup>               |                | 2              | 24 BPP Packe   | d              |                  |

| Port<br>Bit                 | SWAP<br>NIB=0 | SWAP<br>NIB=1   | 8 BPP    | 555 Sparse<br>or Direct<br>Color | 555 CON-<br>TIG | 565 Sparse<br>or Direct<br>Color | 565 Contig     | 1st Access     | 2nd Access     | 3rd Access     | 32 BPP           |

| 0                           | В0            | A0              | A0       | A3BLU                            | A0BLU           | A3BLU                            | A0BLU          | A0BLU          | CORED          | F0GRN          | A0BLU            |

| 1                           | B1            | A1              | A1       | A4BLU                            | A1BLU           | A4BLU                            | A1BLU          | A1BLU          | C1RED          | F1GRN          | A1BLU            |

| 2                           | B2            | A2              | A2       | A5BLU                            | A2BLU           | A5BLU                            | A2BLU          | A2BLU          | C2RED          | F2GRN          | A2BLU            |

| 3                           | В3            | A3              | A3       | A6BLU                            | A3BLU           | A6BLU                            | A3BLU          | A3BLU          | C3RED          | F3GRN          | A3BLU            |

| 4                           | A0            | В0              | A4       | A7BLU                            | A4BLU           | A7BLU                            | A4BLU          | A4BLU          | C4RED          | F4GRN          | A4BLU            |

| 5                           | A1            | B1              | A5       | A3GRN                            | A0GRN           | A2GRN                            | A0GRN          | A5BLU          | C5RED          | F5GRN          | A5BLU            |

| 6                           | A2            | B2              | A6       | A4GRN                            | A1GRN           | A3GRN                            | A1GRN          | A6BLU          | C6RED          | F6GRN          | A6BLU            |

| 7                           | A3            | B3              | A7       | A5GRN                            | A2GRN           | A4GRN                            | A2GRN          | A7BLU          | C7RED          | F7GRN          | A7BLU            |

| 8                           | D0            | C0              | B0       | A6GRN                            | A3GRN           | A5GRN                            | A3GRN          | A0GRN          | D0BLU          | F0RED          | A0GRN            |

| 9<br>10                     | D1<br>D2      | C1<br>C2        | B1<br>B2 | A7GRN<br>A3RED                   | A4GRN<br>A0RED  | A6GRN                            | A4GRN<br>A5GRN | A1GRN<br>A2GRN | D1BLU<br>D2BLU | F1RED<br>F2RED | A1GRN            |

| 11                          | D2<br>D3      | C2              | B3       | A4RED                            | AIRED           | A7GRN<br>A3RED                   | AORED          | A2GRN<br>A3GRN | D2BLU<br>D3BLU | F3RED          | A2GRN<br>A3GRN   |

| 12                          | CO            | D0              | B4       | A5RED                            | A2RED           | A4RED                            | A1RED          | A4GRN          | D4BLU          | F4RED          | A4GRN            |

| 13                          | C1            | D1              | B5       | A6RED                            | A3RED           | A5RED                            | A2RED          | A5GRN          | D5BLU          | F5RED          | A5GRN            |

| 14                          | C2            | D2              | B6       | A7RED                            | A4RED           | A6RED                            | A3RED          | A6GRN          | D6BLU          | F6RED          | A6GRN            |

| 15                          | C3            | D3              | В7       | (NOTE 4)                         | UNUSED          | A7RED                            | A4RED          | A7GRN          | D7BLU          | F7RED          | A7GRN            |

| 16                          | F0            | E0              | C0       | B3BLU                            | B0BLU           | B3BLU                            | B0BLU          | A0RED          | D0GRN          | G0BLU          | A0RED            |

| 17                          | F1            | E1              | C1       | B4BLU                            | B1BLU           | B4BLU                            | B1BLU          | A1RED          | D1GRN          | G1BLU          | A1RED            |

| 18                          | F2            | E2              | C2       | B5BLU                            | B2BLU           | B5BLU                            | B2BLU          | A2RED          | D2GRN          | G2BLU          | A2RED            |

| 19                          | F3            | E3              | C3       | B6BLU                            | B3BLU           | B6BLU                            | B3BLU          | A3RED          | D3GRN          | G3BLU          | A3RED            |

| 20                          | E0            | F0              | C4       | B7BLU                            | B4BLU           | B7BLU                            | B4BLU          | A4RED          | D4GRN          | G4BLU          | A4RED            |

| 21                          | E1            | F1              | C5       | B3GRN<br>B4GRN                   | B0GRN<br>B1GRN  | B2GRN                            | B0GRN          | A5RED          | D5GRN          | G5BLU          | A5RED            |

| 22<br>23                    | E2<br>E3      | F2<br>F3        | C6<br>C7 | B4GRN<br>B5GRN                   | B2GRN           | B3GRN<br>B4GRN                   | B1GRN<br>B2GRN | A6RED<br>A7RED | D6GRN<br>D7GRN | G6BLU<br>G7BLU | A6RED<br>A7RED   |

| 24                          | H0            | G0              | D0       | B6GRN                            | B3GRN           | B5GRN                            | B3GRN          | B0BLU          | D0RED          | GOGRN          | (NOTE 4)         |

| 25                          | H1            | G1              | D1       | B7GRN                            | B4GRN           | B6GRN                            | B4GRN          | B1BLU          | D1RED          | G1GRN          | UNUSED           |

| 26                          | H2            | G2              | D2       | B3RED                            | B0RED           | B7GRN                            | B5GRN          | B2BLU          | D2RED          | G2GRN          | UNUSED           |

| 27                          | НЗ            | G3              | D3       | B4RED                            | B1RED           | B3RED                            | B0RED          | B3BLU          | D3RED          | G3GRN          | UNUSED           |

| 28                          | G0            | H0              | D4       | B5RED                            | B2RED           | B4RED                            | B1RED          | B4BLU          | D4RED          | G4GRN          | UNUSED           |

| 29                          | G1            | H1              | D5       | B6RED                            | B3RED           | B5RED                            | B2RED          | B5BLU          | D5RED          | G5GRN          | UNUSED           |

| 30                          | G2            | H2              | D6       | B7RED                            | B4RED           | B6RED                            | B3RED          | B6BLU          | D6RED          | G6GRN          | UNUSED           |

| 31                          | G3            | НЗ              | D7       | (NOTE 4)                         | UNUSED          | B7RED                            | B4RED          | B7BLU          | D7RED          | G7GRN          | UNUSED           |

| 32                          | J0            | I0              | E0       | C3BLU                            | C0RED           | C3BLU                            | C0BLU          | B0GRN          | E0BLU          | G0RED          | B0BLU            |

| 33                          | J1            | I1              | E1<br>E2 | C4BLU                            | C1BLU<br>C2BLU  | C4BLU                            | C1BLU<br>C2BLU | B1GRN<br>B2GRN | E1BLU          | G1RED          | B1BLU<br>Bablu   |

| 34<br>35                    | J2<br>J3      | I2<br>I3        | E2<br>E3 | C5BLU<br>C6BLU                   | C2BLU<br>C3BLU  | C5BLU<br>C6BLU                   | C2BLU<br>C3BLU | B3GRN          | E2BLU<br>E3BLU | G2RED<br>G3RED | B2BLU<br>B3BLU   |

| 36                          | 10            | JO              | E4       | C7BLU                            | C4BLU           | C7BLU                            | C4BLU          | B4GRN          | E4BLU          | G4RED          | B4BLU            |

| 37                          | I1            | J1              | E5       | C3GRN                            | COGRN           | C2GRN                            | COGRN          | B5GRN          | E5BLU          | G5RED          | B5BLU            |

| 38                          | 12            | J2              | E6       | C4GRN                            | C1GRN           | C3GRN                            | C1GRN          | B6GRN          | E6BLU          | G6RED          | B6BLU            |

| 39                          | 13            | J3              | E7       | C5GRN                            | C2GRN           | C4GRN                            | C2GRN          | B7GRN          | E7BLU          | G7RED          | B7BLU            |

| 40                          | L0            | K0              | F0       | C6GRN                            | C3GRN           | C5GRN                            | C3GRN          | B0RED          | E0GRN          | H0BLU          | B0GRN            |

| 41                          | L1            | K1              | F1       | C7GRN                            | C4GRN           | C6GRN                            | C4GRN          | B1RED          | E1GRN          | H1BLU          | B1GRN            |

| 42                          | L2            | K2              | F2       | C3RED                            | C0RED           | C7GRN                            | C5GRN          | B2RED          | E2GRN          | H2BLU          | B2GRN            |

| 43                          | L3            | K3              | F3       | C4RED                            | C1RED           | C3RED                            | C0RED          | B3RED          | E3GRN          | H3BLU          | B3GRN            |

| 44                          | K0            | L0              | F4       | C5RED                            | C2RED           | C4RED                            | C1RED          | B4RED          | E4GRN          | H4BLU          | B4GRN<br>B5CRN   |

| 45                          | K1            | L1              | F5       | C6RED                            | C3RED           | C5RED                            | C2RED<br>C3RED | B5RED<br>B6RED | E5GRN<br>E6CRN | H5BLU          | B5GRN<br>B6CRN   |

| 46<br>47                    | K2<br>K3      | L2<br>L3        | F6<br>F7 | C7RED<br>(NOTE 4)                | C4RED<br>UNUSED | C6RED<br>C7RED                   | C3RED<br>C4RED | B6RED<br>B7RED | E6GRN<br>E7GRN | H6BLU<br>H7BLU | B6GRN<br>B7GRN   |

| 48                          | N0            | M0              | G0       | D3BLU                            | DOBLU           | D3BLU                            | D0BLU          | COBLU          | E0RED          | H0GRN          | B0RED            |

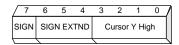

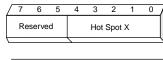

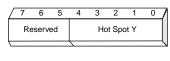

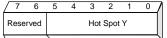

| 49                          | N1            | M1              | G1       | D4BLU                            | D1BLU           | D4BLU                            | D1BLU          | C1BLU          | E1RED          | H1GRN          | B1RED            |